You can add any HTML here

We suggest you to create a Saved Template in Dashboard -> Templates -> Saved Templates and use it by switching content type above to Saved template.

Add anything you want via Header Builder

Take 30% off when you spend $120

Free 2-days standard shipping on orders $255+

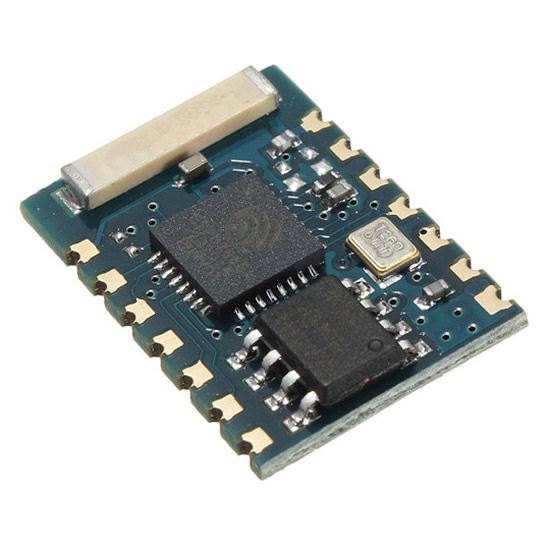

ESP8266 ESP-03 Wifi Module

300.00৳ Original price was: 300.00৳ .250.00৳ Current price is: 250.00৳ .

ESP-03 is a wifi module with its own GPIO pins.

🔥 12 items sold in last 3 hours

14 people are viewing this product right now

Category: Development Board

Tag: ESP8266 ESP-03 Wifi Module

Pin configuration:

| Pin | Name | Alternate Functions | Notes |

| 1 | GND | (Pin 1 is in the corner close to the xtal and away from antenna) | |

| 2 | NC | ||

| 3 | UTXD | SPICS1, GPIO1, CLK_RTC | Typically used as serial uart0 TX |

| 4 | URXD | I2SO_DATA, GPIO3, CLK_XTAL | Typically used as serial uart0 RX |

| 5 | GPIO16 | XPD_DCDC, RTC_GPIO0, EXT_WAKEUP, DEEP SLEEP | Connected to XPD_DCDC ESP pin, can also be connected to ESP EXT_RSTB (reset) pin by closing jumper near pin 8; Reset pin is active low and has an internal weak pull-up; Connecting jumper is required to wake-up ESP from deep-sleep: RTC produces a pulse on XPD_DCDC pin that needs to be fed into EXT_RSTB pin |

| 6 | CH_PD | Power-down: low input powers down the chip, high powers up; tie high for normal operation, or module will not function | |

| 7 | ANT | Wi-Fi antennae does not connect | |

| 8 | VCC | 3.3V input (pin 8 is between the antenna and ESP chip) | |

| 9 | GPIO14 | MTMS, I2SI_WS, SP_CLK | |

| 10 | GPIO12 | MTDI, I2SI_DATA, MISO | |

| 11 | GPIO13 | MTCK, I2SI_BCK, MOSI | |

| 12 | GPIO15 | MTDO, I2SO_BCK, SP_CS | At boot: must be low to enter flash or normal boot (high enters special boot modes) |

| 13 | GPIO2 | I2SO_WS, U1TXD, U0TXD | At boot: must be high to enter flash or normal boot (low enters special boot modes); Typically is used as uart1 TX for debug logging |

| 14 | GPIO0 | SPICS2, CLK_OUT | At boot: low causes the bootloader to enter flash upload mode; high causes normal boot |

Only logged in customers who have purchased this product may leave a review.

Related products

Sale

PIC16F877A Development Board

Sale

Papilio One-500K FPGA

Sale

Open103R Standard, STM32F1 Development Board

Sale

HYDRA Development Kit

Sale

Raspberry Pi Camera Module 2

More

More

Reviews

There are no reviews yet.